凡依照UEFI論壇規範,使用C語言寫作的BIOS即為UEFI BIOS

EFI Shell常用指令

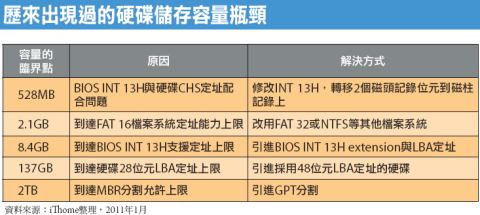

傳統MBR格式的磁碟分割,是透過32位元來描述磁碟的起始點和大小,最高只支援2.2TB的磁碟容量(512bytes x 2 ^ 32磁區)和4個主要分割區。

而UEFI支援的GPT磁碟分割,使用64位元數值來描述分割區,最高支援1680萬TB的磁碟大小及100個主要分割區。512Bytes x 2^64 = 2^3 x 2^70

傳統BIOS開機流程

1. 初始化:

當電腦打開,CPU會自行重置為初始狀態,準備運作。BIOS boot block(基本輸出輸入系統開機區塊)初始化階段啟動,因為此時系統記憶體中是空的,沒有內容可以執行,所以廠商讓CPU去尋找系統BIOS ROM中的reset vector(重置向量):用一個固定的位置來啟動所謂的BIOS boot program開機程式。

一般來說程式會在記憶體的FFFF0h位址,也就是在UMA(上層記憶區域)靠結尾的地方。為避免ROM大小改變造成相容性的問題,所以一般會選擇放這裡。它的內容只有一個jump指令,進一步跳到真正的BIOS啟動程序。當然了,各家IBV (independent BIOS vender;獨立BIOS供應商)可以把程式放在不同的位置,只要透過jump來指定就可以了。

在這段期間,系統的CPU、晶片組、Super I/O和USB只有部分初始化,僅獲取足夠資料來應付萬一BIOS開機失敗,可以利用軟碟(由Super I/O控管)甚至是光碟(由晶片組的IDE/SATA)等儲存媒體來救援BIOS的boot block。

2. POST(Power On Self

Test;開機自我檢測):

然後BIOS開始施行Power-On Self Test(POST;開機自我檢測),在過程中檢查電腦各項組件及其設定,像是:中央處理器、主記憶體、鍵盤、滑鼠等等狀態。接著便尋找被內建在BIOS內部的顯示卡程序並執行。

它通常被放在記憶體C0000h的位置,作用是顯示卡的初始化,而大部分的顯示卡都會在顯示器上顯示其相關訊息。這就是為何各位在開機的時候,首先會在顯示器的畫面左上角出現有關顯示卡訊息的原因。

再下來就是讓BIOS尋找其他裝置的ROM(唯讀記憶體),看看這些設備中哪些還有個別的BIOS。如果這時有找到任何其它裝置的BIOS,它們也會被執行。

下一步BIOS會顯示啟動畫面,並開始更深入的檢測,包含我們平常可以在螢幕上看到的記憶體容量檢測。如果這時候遇到任何錯誤,就會在畫面上顯示錯誤訊息。

3. 記錄電腦系統的設定值:

到這裡還沒有結束,再來BIOS會根據自己的「系統資源表」,來對系統進行進一步的確認,看看你的電腦究竟安裝了那些系統資源或設備。有些電腦會逐步顯示這些被偵測到的設備。例如BIOS支援隨插即用,那它將會偵測和配置隨插即用裝置,並顯示由BIOS偵測到的隨插即用設備。

在這些檢測結束後,BIOS會打出一個偵測總結表於畫面上。而這個總結表在部分IBV的設定中是可以讓使用者開啟或關閉的。當然也有些IBV為加速開機把這一步直接隱藏省略。

Tips:BIOS boot block

在快閃唯讀記憶體內,通常會分成兩個區塊,一個區塊存放一般的BIOS程式碼,即所謂的code block(程式碼區塊);另一個區塊則是存放用來開機(或急救)的程式碼,就是所謂的boot block(開機區塊)。當電源打開時,主機板會先從boot block執行,它會立即檢查code block 的程式碼是否正確,如果正確,就會轉到code block 繼續執行下去。而所謂的BIOS recovery(BIOS回復)就是利用boot block回寫動作來進行BIOS更新失敗時的救援。

4. 提供常駐程式:

提供作業系統或應用程式呼叫的中斷向量,如INT 10h(VGA圖形及文字輸出中斷)等。

5. 載入作業系統:

到這裡是系統檢測的部分,接下來BIOS便開始尋找開機裝置,使用者可以透過在BIOS的設定來決定搜尋順序,目前常見的開機設備至少包含FDD、HDD以及光碟機和USB開機裝置等多項。

找到開機裝置後,BIOS將會搜尋開機訊息以進行作業系統的開機過程。如果是找到了一個灌好OS的硬碟,它將會尋找位在硬碟第0面,第0軌,第1磁區裡的Master Boot Record(主要開機磁區)。如果它找到的是FDD,也會讀取軟碟的第1磁區。再把讀取到的資料放在記憶體7C00h的位置,跳到那裡並且執行它。自此才開始進入OS啟動階段。

UEFI BIOS系統的開機流程

1. SEC階段:

SEC(安全性)階段其主要的特色為「cache as RAM」,即處理器的快取當成記憶體。由於C語言需要使用堆疊,在這個階段的系統記憶體尚未被初始化,在沒有記憶體可用的情況下,便把處理器的快取當成記憶體來使用,在主記憶體被初始化之前來進行預先驗證CPU/晶片組及主機板。

因為這時侯沒有快取,會導致處理器的效能變得較差,所以在記憶體初始化完畢之前,SEC和PEI階段的程式碼越簡短,越能減少這個副作用。

2. PEI階段:

和傳統BIOS的初始化階段類似,PEI(EFI前初始化)階段是用以喚醒CPU及記憶體初始化。這時候只起始了一小部分的記憶體。同時,晶片組和主機板也開始初始化。接下來的服務程式會確定CPU晶片組被正確的初始化,在此時,EFI驅動程式派送器將載入EFI驅動程式記憶體,進入了起始所有記憶體的DXE階段(驅動程式執行環境)。

3. DXE階段:

DXE的主要功能在於溝通EFI驅動程式及硬體。也就是說此階段所有的記憶體、CPU(在此是指實體兩個或以上的非核心數目,也就是雙CPU插槽處理器甚至是四CPU插槽處理器)、PCI、USB、SATA和Shell都會被初始化。

4. BDS階段:

在BDS(開機設備選擇)這個階段,使用者就可以自開機管理者程式頁面,選擇要從哪個偵測到的開機設備來啟動。

5. TSL階段:

然後進入TSL(短暫系統載入)階段,由作業系統接手開機。除此之外,也可以在BDS階段選擇UEFI Shell,讓系統進入簡單的命令列,進行基本診斷和維護。

傳統BIOS哪裡不好?

1. 過時的16位元模式

在x86系列CPU進入32位元的時代,為了相容性考量,當時最新的80386 CPU保留了16位元的執行方式,即真實模式(real mode)。在後來多次的CPU改朝換代中都保留了這種執行方式,甚至在含有EM64T的Xeon系列CPU中,供電到CPU啟動時仍然會切換到16位元的真實模式下執行。

也就是說,雖然各大BIOS廠商為了配合潮流演進,將許多新功能新元素添加到產品中,但BIOS在本質上沒有任何改變。迫使Intel在開發更新的CPU時,都必須加進會使效能大大降低的相容模式。

2. 只有1MB定址空間

各位讀者如果有注意傳統BIOS開機,在POST完畢後螢幕上打出的系統摘要表,會發現記憶體欄位標示著「Base Memory=640KB」。加上前一篇提到的384KB UMA(這裡的記憶體不會列入Base Memory),就是所謂1MB可定址記憶體空間。

會造成這項限制,主要還是真實模式的副作用。16位元的CPU,其定址能力為20條定址線所能處理的2^20位元組(Bytes),也就是1024千位元組(KB)。換句話說,在進入OS之前的開機階段,即使安裝了高達4GB的記憶體,絕大部分都無法使用。

2^20 Byte = 2^10 x 2^10 = 1 MB

IBM推出的第一台PC机采用的CPU是8088晶元,它只有20根地址线,也就是说,它的地址空间是1MB。

PC机的设计师将1MB中的低端640KB用作RAM,供DOS及应用程式使用,高端的384KB则保留给ROM、视频适配卡等系统使用。从此,这个界限便被确定了下来并且沿用至今。低端的640KB就被称为常规记忆体即PC机的基本RAM区。

在1985年初,Lotus、Intel和Microsoft三家共同定义了LIM-EMS(Expanded

Memory Spec,即扩充记忆体规范,通常称EMS为扩充记忆体。

我们把1MB以上的地址空间称为扩展记忆体XMS(eXtend

memory)

在386以上档次的微机中,有两种存储器工作方式,一种称为实地址方式或实方式,另一种称为保护方式。在实方式下,物理地址仍使用20位,所以最大定址空间为1MB,以便与8086相容。保护方式采用32位物理地址,定址范围可达4GB。

OS系统在实方式下工作,它管理的记忆体空间仍为1MB,因此它不能直接使用扩展存储器。为此,Lotus、Intel、AST及Microsoft公司建立了MS-DOS下扩展记忆体的使用标准,即扩展记忆体规范XMS。我们常在Config.sys文件中看到的Himem.sys就是管理扩展记忆体的驱动程式。

1MB以上空间的第一个64KB。我们把它称为高端记忆体区HMA(High Memory Area)。HMA的物理存储器是由扩展存储器取得的。因此要使用HMA,必须要有物理的扩展存储器存在。

UMB(Upper Memory Blocks)称为上位记忆体或上位记忆体块。它是由挤占保留记忆体中剩馀未用的空间而产生的,它的物理存储器仍然取自物理的扩展存储器,它的管理驱动程式是EMS驱动程式。

3. 組合語言難維護

假設某天你買了一張高階工作站主機板,再裝上一張SCSI或SAS的磁碟陣列卡,竟然發現安裝後你的主機板開機開不下去,然後顯示「Not enough space to copy PCI option ROM」或「Option ROM memory space exhausted」警告字串。然後本來你那雀躍快樂的心情消失了,取而代之的是「歸LP火」熊熊燃燒著。

當你打電話給陣列卡商,電話那頭的死公務員聲音說著:「你要不要問問主機板廠有沒有新的BIOS?」。 好不容易找上主機板廠商客服問:「你們有沒有辦法解決?」然後,你和主機板BIOS工程師之間的攻防就此展開。

對板卡廠的BIOS工程師而言,除非剛好有下單下很大的客戶遇到類似相關問題,否則很有可能就是不了了之。你只好趁購買七天內退掉那張陣列卡,不然就是再找一張可以正常搭配的主機板。

由於傳統BIOS是用組合語言編寫的,而軟體界早就已經是C/C++高階語言甚至是.NET滿天飛,為了相對難找的人才(組合語言高手相對少,要BIOS真正寫得好的更是少數)來減緩新產品上市的速度,不管是消費者或廠商都無法接受。

此時UEFI BIOS標準化和模組化的特徵,便可加速產品推出和減少debug的時間。另外C語言寫的UEFI BIOS體積也會變大,連帶使儲存BIOS的EEPROM需要擴增。

別忘了,這也是Intel的勢力範圍,如果EFI BIOS推廣成功,板卡廠就得多採購一顆晶片。

4. 十年不變的程式碼

上述三大問題是以開發廠商的角度來觀察。其他隱而不現的部分,則包含了功能的侷限性和對使用者不夠友善的操作介面。對照現今的視窗介面作業系統,傳統BIOS以文字介面為主且充滿著火星文,加上除了單純的開機,作為仲介硬體初始化和作業系統的功能外實在陽春的可憐。

在開發Itanium CPU之際,業界大魔王Intel實在不想再受制於這些顧慮。試想,既然這是一個新生的CPU架構,那系統韌體和作業系統之間的介面就順便一起重新定義。

並且這一次,Intel為了讓以後各種新的規格和技術可以快速導入,嚴格定義這個傳統BIOS接班人必須具有擴展彈性,而且採取標準化的韌體介面規範,以避免發生傳統BIOS的IBV程式碼更新太被動的問題。

UEFI BIOS哪裡好?

1. 定址空間更彈性

UEFI BIOS利用載入EFI driver的形式,來進行硬體的辨識/控制及系統資源掌控。

傳統BIOS是以真實模式中斷向量的方式增加硬體功能。它要將一段類似於驅動程式的16位元代碼,放置在記憶體0x000C0000至0x000DFFFF之間。這段記憶體空間有限(128KB),因此,當必須放置的option ROM超過128KB時,傳統BIOS便無能為力。

DFFFF-C0000=1FFFF=2

x 2^16=2^7 x 2^10=128KB

很多時候傳統BIOS的工程師為了解決這類問題,像剛剛提到的介面卡BIOS容量過大,便要想辦法利用可能的排列組合硬擠出空間來放驅動代碼。而重組過程有時不小心造成一些副作用,例如才剛解決的bug,重組後又再發生!也就是說,UEFI BIOS可以更有系統的分配儲存空間,避免使用強制定址。

2. 什麼系統都能用

另外,傳統BIOS的硬體服務程式都是以16位元代碼的形式存在,在增強模式下執行的作業系統想存取這些服務會有困難。因此BIOS提供的服務在現實中只能提供給MS-DOS之類的系統用。

相對的,UEFI系統下的驅動並不是可以直接在CPU執行的代碼,而是用EBC(EFI Byte Code)這種專用於EFI driver的虛擬機器指令,該指令必須在UEFI的DXE階段被解壓縮後翻譯執行。

如此便有更佳的向下相容性,因為EFI driver是彈性的驅動程式模組架構,可不斷的擴充驅動程式及介面,不用重新編寫,所以就無需考慮因系統升級所衍生的相容性因素。

3. 開發維護更容易

加上EFI driver開發簡單,所有的PC零組件廠商都可以參與,就像現代作業系統的開發模式,這樣的模式曾使Windows系統短短幾年就變得無比強大。有了EFI driver,也可以讓顯示卡在開機階段就載入某種程度的功能,進而可以把傳統文字介面為主的BIOS轉成圖形介面。

4. 精簡系統用途大

最後還有EFI Shell,這是個精簡的作業系統,可以讓使用者進行BIOS的更新、系統診斷、安裝特定軟體。有了UEFI BIOS甚至可以播放CD和DVD而不需完全載入OS,EFI driver可以被載入或卸載,連TCP/IP核心程式都可以使用。基於EFI的driver model可使UEFI系統接觸到所有的硬體功能,在進入作業系統之前瀏覽網站不再是天方夜譚,甚至實作起來也非常簡單。總之,對使用者而言,多了一個方便的環境以及華麗的圖形介面,是最明顯的好處。

UEFI由以下幾個部分所組成:

1.Pre-EFI初始化模組

2.EFI驅動執行環境(DXE)

3.EFI驅動程式

4.兼容性支援模組(CSM)

5.EFI高層應用

6.GUID磁碟分割表(GPT)

解決MBR分割所帶來的2TB限制問題。理論上可支援高達9.4ZB的磁碟分割區